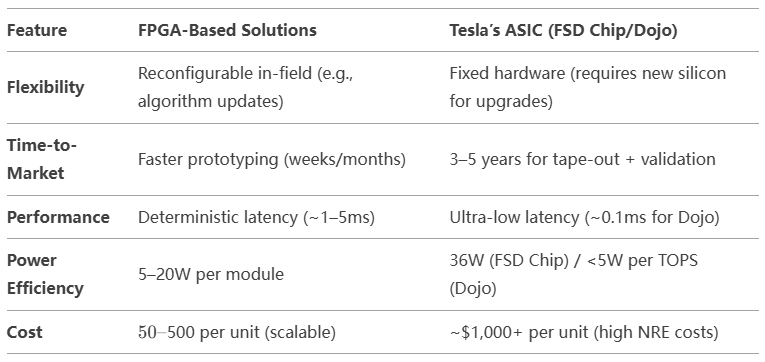

Tesla’s shift from FPGA/GPU-based systems to custom ASICs (e.g., FSD Chip, Dojo D1) represents a strategic divergence from industry norms. Here’s how FPGA solutions compare to Tesla’s approach in LiDAR/vision processing:

1. Architectural Comparison

2. Sensor Processing Capabilities

FPGAs (e.g., Xilinx for LiDAR)

Strengths:

- Handle multi-sensor fusion (LiDAR + radar + cameras) with parallel pipelines.

- Support legacy protocols (CAN FD, Automotive Ethernet).

Weaknesses:

- Higher power than ASICs for equivalent TOPS.

- Limited AI acceleration (vs. dedicated NPUs).

Tesla’s ASICs (Vision-Only)

Strengths:

- Custom SRAM-on-chip (32MB cache for FSD Chip) reduces DRAM latency.

- Dojo’s 1.1 EFLOPS supercomputer trains vision models at scale.

Weaknesses:

- No native LiDAR/radar support (relies purely on cameras).

- Inflexible to new sensor modalities (e.g., 4D radar).

3. Real-World Implementations

FPGA Examples:

- Luminar Iris (Xilinx FPGA): Processes 200m+ LiDAR data for Volvo.

- Continental ARS540 (Xilinx RFSoC): 4D imaging radar with MIMO processing.

Tesla’s ASIC Examples:

FSD Chip (HW3/HW4):

- 144 TOPS (HW3) → 256 TOPS (HW4) for 8-camera vision pipelines.

- Uses dual NPUs for transformer-based “HydraNet” models.

Dojo D1 Tile:

- 362 TFLOPS (FP32) for autonomous training.

- 1.25TB/s bandwidth via custom interconnect.

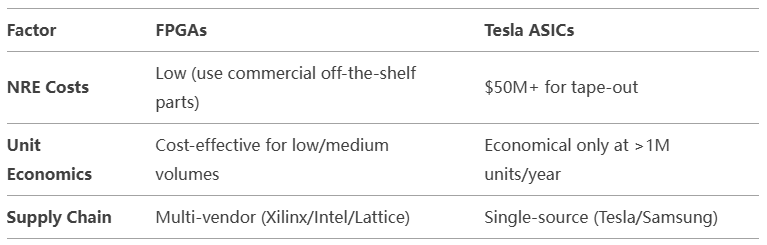

4. Cost & Scalability

5. Future-Proofing

- FPGAs: Better for evolving standards (e.g., transitioning to 4D LiDAR or neuromorphic radars).

- ASICs: Tesla’s vertical integration allows tight hardware-software co-design (e.g., optimizing for “BEV transformers”).

Key Takeaways

- For Sensor-Agnostic Systems: FPGAs win (used by 90% of LiDAR/radar vendors).

- For Vision-Only Scale: Tesla’s ASICs are unbeatable in performance/power.

- Hybrid Future: Startups like SiFive are blending FPGA-like programmability with ASIC efficiency.

Tesla’s Lesson: ASICs only make sense if:

- You control the entire stack (sensors → algorithms).

- Your volume justifies NRE costs.

- You’re willing to freeze architectures for 5+ years.

FPGA vs. ASIC Decision Flowchart

plaintext

┌───────────────────────┐

│ Need sensor flexibility? │

└──────────┬─────────────┘

│

┌───────────────▼────────────────┐

│ │

┌────────▼───────┐ ┌─────────▼─────────┐

│ Choose FPGA │ │ Choose ASIC │

│ (Luminar, BMW)│ │ (Tesla, Apple) │

└────────────────┘ └───────────────────┘